[더구루=정예린 기자] 삼성전자가 핵심 파트너사인 미국 '케이던스'와 손잡고 파운드리(반도체 위탁생산) 생태계 구축에 속도를 낸다. 세계 최초 양산한 게이트올어라운드(GAA) 기반 3나노미터(nm) 공정 설계를 검증할 맞춤형 솔루션을 도입, 고객 편의성과 생산성을 강화한다.

30일 케이던스에 따르면 케이던스는 최근 자사 설계 검증 솔루션 '콴터스 FS'를 삼성전자 파운드리 △3나노 GAA 1세대 △3나노 △4나노 공정에 사용할 수 있다는 인증을 확보했다. 양사는 이번 협력을 통해 삼성전자의 최첨단 공정 채택률이 높아질 것으로 기대하고 있다.

콴터스 FS는 케이던스의 최신 3D 필드 솔버다. 필드 솔버는 반도체 설계 검증 자동화 툴(EDA) 일환이다. 반도체 커패시턴스와 저항 변화 등은 물론 칩 설계 전반에 중요한 요소들을 미리 시뮬레이션 할 수 있는 소프트웨어다. 삼성전자에 앞서 TSMC도 자사 3나노 공정에 콴터스 FS를 적용했다.

삼성전자 파운드리 고객은 콴터스 FS를 이용해 공정 정확성과 생산 효율성을 높여 제품의 시장 출시 시간을 단축시킬 수 있다. 한 번에 많은 설계를 빠르게 검증 가능해 테이프아웃(칩 설계를 최종적으로 마친 상태) 기한을 맞출 수 있다는 게 케이던스의 설명이다. 콴터스 FS는 최대 1000개의 칩을 동시에 처리한다.

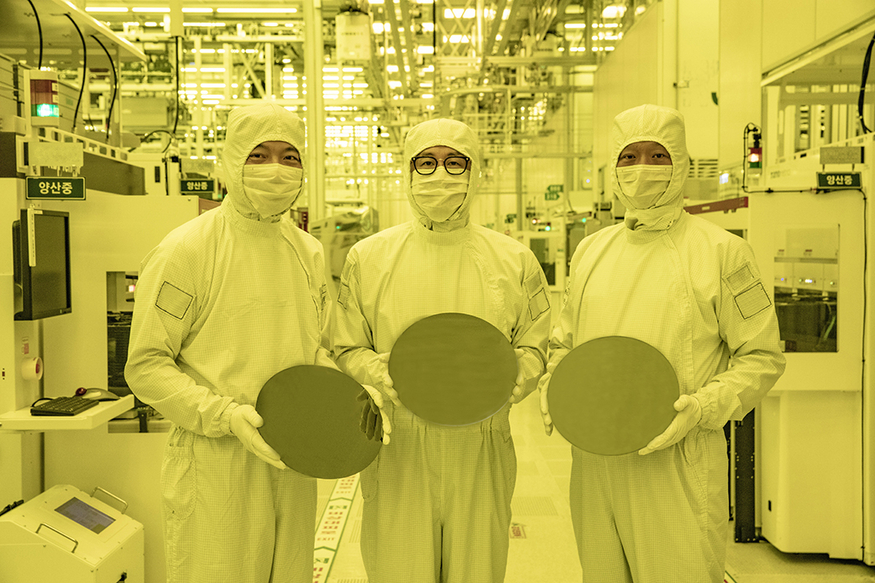

삼성전자는 지난해 6월 3나노 GAA 1세대 공정 기반 칩을 첫 양산했다. 3나노 공정에 GAA 기술을 적용한 반도체 기업은 삼성전자가 유일하다. TSMC는 2나노부터 GAA 공정을 도입할 예정인 것으로 전해진다.

3나노 GAA 2세대 공정 기반 반도체 생산 계획도 순항하고 있다. 3나노 칩 양산을 두 차례 미룬 뒤 12월 말에 부랴부랴 첫 3나노 칩을 양산한 TSMC와 대조된다.

삼성전자는 작년 2분기 실적발표 컨퍼런스콜에서 "3나노 GAA 2세대 공정은 2024년 양산을 목표로 계획대로 진행중"이라며 "모바일 응용처에서 복수의 대형 고객사를 이미 확보했으며, 다수의 HPC(고성능 컴퓨팅), 모바일 고객과 수주 관련 논의도 하고 있다"고 밝힌 바 있다.

삼성전자는 오는 2024년 3나노 GAA 2세대를 시작으로 2025년 2나노 GAA, 2027년 1.4나노 GAA 공정 기반 칩 양산이라는 차세대 파운드리 사업 로드맵을 발표했다. 이를 통해 파운드리 1위 업체 TSMC와의 점유율 격차를 좁히고 시장 입지를 확대한다는 목표다.

이성재 삼성전자 파운드리사업부 디자인 플랫폼 개발실 상무는 "케이던스는 복잡한 GAA 모델링 기능에 대한 깊은 전문 지식을 가지고 있으며 우리의 성능 요구 사항을 빠르고 정확하게 수용한다"며 "케이던스와의 지속적인 협력을 통해 상호 고객에 고급 공정에 대한 새로운 기술을 전달할 수 있게 됐다"고 강조했다.

비벡 미슈라 케이던스 디지털·사인오프그룹 부사장은 "초기 기술 개발 과정에서 삼성 파운드리와 협력해 콴터스 FS 솔루션에서 모든 요구 사항을 충족하고 구현, 고객이 공정 기술을 쉽고 빠르게 채택할 수 있도록 했다"며 "고객을 지원하는 가장 좋은 방법은 효율성을 제공해 혁신적인 제품을 출시하도록 돕는 것"이라고 전했다.