[더구루=오소영 기자] 세계 최대 반도체 연구소 IMEC가 1나노미터(㎚·1㎚는 10억분의 1m) 이하 반도체의 청사진을 공유했다. 2024년 게이트올어라운드(GAA) 기반의 2나노 칩, 2030년 차기 트랜지스터 구조가 적용된 0.7나노 제품이 출시될 전망이다.

26일 업계에 따르면 IMEC는 최근 벨기에 안트베르펜에서 열린 '퓨처 서밋'에서 1나노 이하 실리콘·트랜지스터 로드맵을 공유했다.

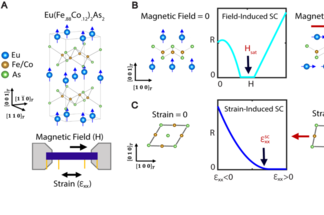

IMEC는 2024년 2나노 제품 출시를 예상했다. 나노시트 구조를 활용한 GAA가 적용된다.

나노시트는 나노와이어처럼 한 줄로 구조물을 만들되 깊이의 제한을 없애 공간 효율이 높은 장점이 있다. GAA는 전류가 흐르는 채널의 4면을 모두 게이트가 감싸고 있어 전류 흐름을 세밀하게 제어할 수 있는 차세대 트랜지스터 구조다. 기존 핀펫(FinFET) 기술보다 칩 면적과 소비전력은 줄이면서 성능은 높일 수 있다.

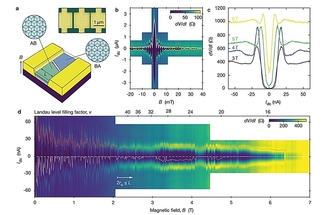

IMEC는 1나노 이하 제품에도 GAA 기술이 쓰일 것으로 내다봤다. 2028년 GAA 기반 1나노, 2030년 0.7나노 제품이 상용화될 전망이다. 다만 나노시트 구조는 포크시트로 대체된다.

2032년에는 0.5나노 칩 출시와 함께 GAA가 CFET(Complementary FET)에 자리를 내줄 것으로 예상된다. CEFT는 다른 전도 유형의 트랜지스터를 교대로 3차원적으로 쌓아 칩 면적을 감소시키는 기술이다.

공정이 미세화되며 네덜란드 ASML의 EUV 장비도 진화할 전망이다. 2나노 제품은 4세대 장비로 만들어지지만 1.4나노부터는 5세대가 활용된다. 4세대 장비로 2나노 이하 반도체를 생산하려면 여러 차례 패터닝하는 다중 패터닝 공정을 거쳐야 하는데 이 경우 생산성이 저하되고 공정 수가 늘어나는 만큼 시간과 비용이 증가하는 문제가 있다.

ASML은 렌즈 크기를 0.33NA(4세대)에서 0.55NA로 키운 5세대 장비(High-NA EUV)를 개발해 이를 해소했다. AMSL은 2026년 대량 생산에 돌입할 것으로 예상하고 있다. 인텔은 반도체 업체 중 가장 먼저 해당 장비를 받기로 했다. 인도 시점은 2025년께다.

IMEC는 2030년 이후 새 재료가 실리콘을 대체하고 2차원적 재료가 등장할 수 있다고 전망했다. 양자 컴퓨팅의 상용화로 자기 기반 게이트(Magnetics-based gates)가 부상할 가능성도 있다.

한편, IMEC는 벨기에 브뤼셀에 있다. 반도체 설계부터 공정, 소자, 시험, 제작 등 모든 공정의 연구개발(R&D)을 지원한다.