[더구루=정예린 기자] 삼성전자가 차세대 3차원(3D) 집적회로(IC) 패키징 기술 개발을 가속화한다. 핵심 파트너사인 미국 '케이던스'의 설계 검증 솔루션을 적용해 고객 편의성과 생산성을 강화하는 등 파운드리(반도체 위탁생산) 생태계 구축에도 앞장선다.

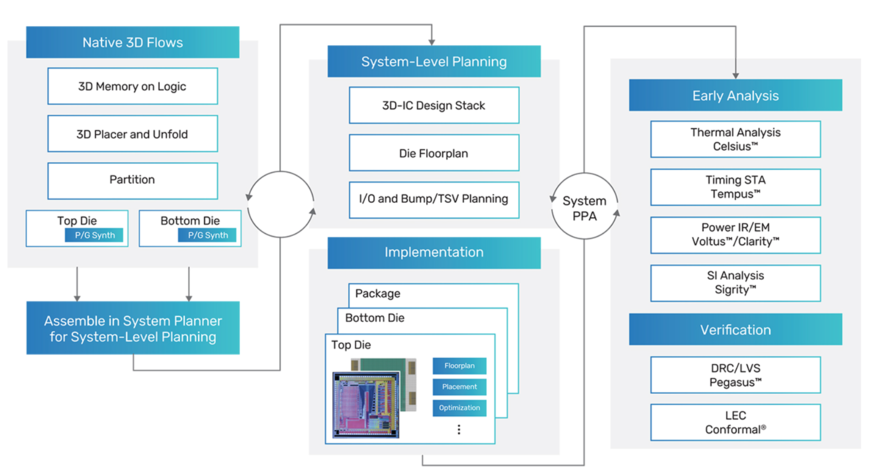

19일 케이던스에 따르면 케이던스는 최근 삼성전자의 3D IC 솔루션에 자사 '인테그리티 3D-IC 플랫폼'을 최적화했다. 양사는 이번 협력을 통해 고객들이 PPA(소비전력·성능·면적) 손실을 최소화할 수 있을 것이라고 보고 있다.

삼성전자는 이달 초 미국 실리콘밸리에서 개최한 '삼성 파운드리 포럼 2022'에서 3나노미터(nm) 공정 게이트올어라운드(GAA) 기술에 MBCFET(Multi Bridge Channel FET) 구조를 적용하는 한편 3D IC 솔루션도 제공, 고성능 반도체 파운드리 서비스를 선보이겠다고 발표한 바 있다.

3D IC 기술은 반도체 3개를 쌓아 올리는 패키징 기술이다. 패키징 기술력이 높으면 같은 칩으로도 더 작고 효율적인 패키지를 꾸릴 수 있다. 반도체 미세공정의 한계로 반도체 성능 향상 폭이 제한되면서 여러 칩을 적층해 성능을 극대화하는 패키징 기술이 주목받고 있다. 하지만 적층된 칩을 연결하는 과정에서 셀 배치, 라우팅 리소스 차단 등의 문제가 발생해왔다.

케이던스의 플랫폼을 사용하면 설계 과정에서 미리 최적의 3D 구조 배치 시나리오를 테스트하는 등 시뮬레이션 할 수 있다. 문제가 발생하면 해당 설계를 분석한 뒤 다시 새로운 방식을 적용하면 된다. 제품 품질과 정확성을 높여 고객들이 설정한 목표를 달성할 수 있도록 돕는다.

김상윤 삼성전자 파운드리사업부 디자인 플랫폼 개발실 상무는 "고급 공정에서 적층 다이 설계를 생성하는 고객은 항상 PPA를 손상시키지 않으면서 당사 기술의 이점을 활용하고 싶어 한다"며 "케이던스와의 협력을 통해 고객들에 PPA를 포기하지 않고 3D 설계를 구축할 수 있는 혁신적인 기술을 고객에게 제공할 수 있게 됐다"고 밝혔다.